# Data sheet **2.5V I/O protection**

Full local protection

UMC 65nm

Sofics has verified its TakeCharge ESD protection clamps on technology nodes between 0.25um CMOS down to 28nm across various fabs and foundries. The ESD clamps are silicon and product proven in more than 1500 mass produced IC-products. The cells provide competitive advantage through improved yield, reduced silicon footprint and enable advanced multimedia and wireless interfaces like HDMI, USB 3.0, SATA, WIFI, GPS and Bluetooth.

The ESD clamp described in this document protects 2.5V domains in UMC 65nm CMOS technology.

## UMC 65nm 2.5V I/O protection

#### Clamp type and usage

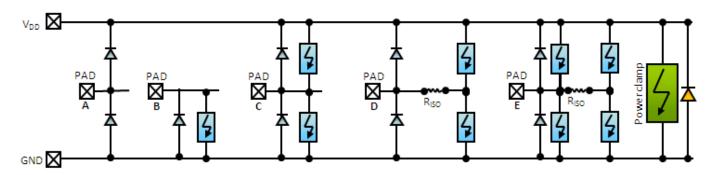

The Sofics ESD cells cover all types of protection concepts and approaches as detailed in the figure below. The ESD clamp cell described in this document is a type C clamp.

| UMC 65nm                         | 2.5V | Comments |

|----------------------------------|------|----------|

| Core Protection                  |      |          |

| Input Protection                 | YES  |          |

| Output Protection                | YES  |          |

| I/O Protection                   | YES  |          |

| Over Voltage Tolerant I/O (OVT)  |      |          |

| Under Voltage Tolerant I/O (UVT) |      |          |

| Inter Domain Protection          |      |          |

#### Stress cases covered

| PAD to VSS | clamp | VSS to PAD | Diode down |

|------------|-------|------------|------------|

| VDD to PAD | Clamp | PAD to VDD | Diode up   |

| VDD to VSS |       | VSS to VDD |            |

#### Connections in the cell

Vdd, Vss, I/O

#### **Features**

- Efficient ESD protection

- > 3.6 kV Human Body Model (HBM)

- > 220 V Machine Model (MM)

- Leakage <10nA measured at 2.75V</li>

- Silicon footprint <4000um²

Sofics Proprietary – ©2012 Page 2

#### **Maximum ratings**

| Rating                          | Symbol          | Value |      | Unit |

|---------------------------------|-----------------|-------|------|------|

|                                 |                 | Min   | Max  |      |

| Supply Voltage Range (DC)       | $V_{DD}$        | -0.3  | 2.75 | V    |

| Input/Output Voltage Range (DC) | V <sub>IO</sub> | -0.3  | 2.75 | V    |

| Operating Temperature           | T <sub>op</sub> | -25   | 125  | °C   |

| Burn-in Voltage (DC @ 125°C)    |                 | 3.75  |      | V    |

Stresses exceeding these maximum ratings may damage the device. Functional operation above the recommended operating conditions is not implied. Extended exposure to stresses above the recommended operating conditions may affect device reliability.

The provided golden cell is designed for these maximum ratings/specifications. If the desired specification level differs, the golden cell has to be scaled up or down by using the Sofics implementation/scaling guidelines to remain a robust and effective ESD protection for the different specifications.

#### **Electrical Characteristics**

T<sub>amb</sub> = 25°C unless stated otherwise

| Parameter                                   | Symbol            | Тур.   | Unit |

|---------------------------------------------|-------------------|--------|------|

| Trigger Voltage                             | V <sub>t1</sub>   | 1.2    | V    |

| Holding Voltage                             | V <sub>h</sub>    | 1.2    | V    |

| Leakage current @ T <sub>amb</sub> = 25 °C  | I <sub>leak</sub> | <10    | nA   |

| Leakage current @ T <sub>amb</sub> = 120 °C | I <sub>leak</sub> |        |      |

| Total Capacitance Load, 0V bias             | C <sub>L</sub>    | 734.06 | fF   |

| Required (for ESD) resistance               | R <sub>iso</sub>  | 0      | Ohm  |

| between bondpad and functional circuit      |                   |        |      |

| HBM – Human Body Model                      |                   | 3.6    | kV   |

| MM – Machine Model                          |                   | 220    | V    |

### Process, Area and integration

• Process: UMC 65nm

• Used Metals: metals – customization service available

Special layers needed: N/A

• Area: 3927.96 um<sup>2</sup> (40.62 um x 96.7 um)

Sofics Proprietary – ©2012 Page 3

Data sheet: UMC 65nm 2.5V I/O protection DS-UM65-C2V5-RC

### **About Sofics**

Sofics (<a href="www.sofics.com">www.sofics.com</a>) is the world leader in on-chip ESD protection. Its patented technology is proven in more than a thousand IC designs across all major foundries and process nodes. IC companies of all sizes rely on Sofics for off-the-shelf or custom-crafted solutions to protect overvoltage I/Os, other non-standard I/Os, and high-voltage ICs, including those that require system-level protection on the chip. Sofics technology produces smaller I/Os than any generic ESD configuration. It also permits twice the IC performance in high-frequency and high-speed applications. Sofics ESD solutions and service begin where the foundry design manual ends.

**ESD SOLUTIONS AT YOUR FINGERTIPS**

## Our service and support

Our business models include

- Single-use, multi-use or royalty bearing license for ESD clamps

- Services to customize ESD protection

- o Enable unique requirements for Latch-up, ESD, EOS

- o Layout, metallization and aspect ratio customization

- o Area, capacitance, leakage optimization

- Transfer of individual clamps to another target technology

- Develop custom ESD clamps for foundry or proprietary process

- Debugging and correcting an existing IC or IO

- ESD testing and analysis

## **Notes**

As is the case with many published ESD design solutions, the techniques and protection solutions described in this data sheet are protected by patents and patents pending and cannot be copied freely. PowerQubic, TakeCharge, and Sofics are trademarks of Sofics BVBA.

## Version

August 2012

Sofics Proprietary – ©2012 Page 4